芯片异构集成中需要解决更多互连和新技术问题

先进封装选项继续在追求“超过摩尔”和更高水平的集成技术。需要解决许多高密度芯片设计互连,以及许多新问题。

芯片行业首次尝试多芯片封装,利用硅通孔(TSVs)的硅插入器来实现实质性的芯片性能提高,尽管它在高频(4-6 GHz)段性能提高有限,而且硅插入器的成本很高。但这刺激了芯片替代方案的产生,如在桥和基板上的高密度扇形输出,每一种都有其优缺点。

为了生产具有多个芯片设计的高产模块,芯片制造商正在扩展现有工艺,充分利用芯片扇出和嵌入式配置。他们也开始解决高级芯片封装的设计挑战,这要求在装配过程中使用PDK(工艺设计套件)。

ASE高级总监曹立红表示:“芯片和异质整合已经成为关键的推动因素。我们看到芯片市场上出现了新的突破。HPC有2.5D硅TSV集成,有高密度的扇出RDL和桥式连接,以及使用3D微凸起和高密度混合键合的die-to-die连接。”

芯片内部互连正在深入研究再分配层的2µm线和空间机制,在先进的硅插入器中,0.65µm可以满足高带宽要求。

从EDA到封装的共同设计

架构的多元化和高级芯片封装的高代价鼓励了芯片设计者和封装公司之间更紧密的协作。EDA公司和OSATs正在开发协作芯片设计工具集,提高软件包的性能,降低成本,并缩短集成软件包的上市时间。

共同开发似乎使封装中的芯片设计工作至关重要,特别是当涉及到组合来自不同公司的芯片时。我们的一位客户说得很好:“不会天生就有3D工程师。2D工程师一夜之间必须成为2.5D和3D工程师。在SoC的世界里,多年来已经开发出了一些方法、参考工艺和PDK,我们已经习惯了它们来做芯片设计。当你把所有这些部件放在一起时,你不能把它看作是一个芯片封装人员的问题或一个硅工程师的问题,必须全面分析它。”

Cadence定制IC和PCB集团的产品管理组主管John Park说:“当我们设计芯片时,我们是基于我们从晶圆厂获得的PDK。晶圆厂的芯片工艺套件,为我们提供了ASIC芯片设计所需要的数据,从而知道这项技术是什么。我们得到了资源库、芯片设计规则和连接验证信息等。我们知道,无论我们在创造什么,我们都将能够组装芯片,因为晶圆厂在指导我们。”

这就需要各种芯片设计、制造,并且芯片封装过程尽可能自动化,这样工程师才能专注于新的芯片设计和能力,而不是把所有的时间都花在一系列许多单独芯片组件的一次性芯片封装上。

Amkor技术公司的芯片/FCBGA集成业务副总裁Mike Kelly说:“这些设计工具越来越接近于单一设计。我们曾经只设计制造单一芯片,花费了所有的时间和验证,因为你在一个芯片里,每个人都知道发生了什么。针对先进芯片封装,在面对多芯片时仍然可以及时考虑方案。3D增加了另一个元素,因为在物理世界中,我们很容易看到三维物体。但是,你如何将其抽象成你所知道的与Verilog或IC设计工具兼容的东西。我不会说它已经百分之百准备好了,但大客户正在实施这项工作。”

更高水平的自动化也将有助于加快质量和共同开发的时间。ASE的Cao说:“对于基底芯片设计的案例,通常你有一个APD文件,它生成Gerber文件,然后你可以路由它。但是高密度的RDL再分配层设计怎么样呢?”

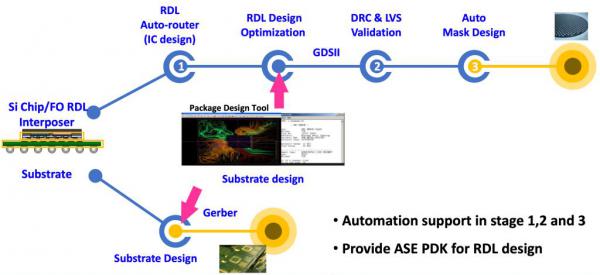

ASE的RDL芯片设计流程使用了三个自动路由步骤。ASE的Cao说:“我们利用芯片封装设计工具来优化RDL的芯片设计。之后,您将生成GDS文件。然后,从GDS文件中执行LVS(布局与原理图)检查和DRC(设计规则检查),最后您将使用自动掩膜设计工具生成光罩。我们的方法可以通过自动路由节省50%的layout时间。”

曹指出,单独使用自动光罩生成器可以将处理时间从三天减少到大约一小时。

图1:封装PDK流程包括三个RDL的自动路由步骤,显著加快了开发时间。来源:ASE

但是,先进芯片封装的共同设计最好是在自己的芯片和封装公司中进行优化,如TSMC、英特尔和UMC。事实上,内部开发的芯片和封装是大批量先进封装的主要方式。

芯片封装中的电气互连数量正在飞速增长。由此而来的是可靠性问题。

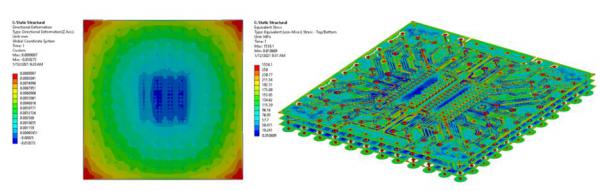

Ansys的产品营销总监马克·斯温宁( Marc Swinnen)说:“现在有很多很多的连接,即使是在一个适度的2.5D芯片设计中,它很容易包含40万到50万个微凸块。因为这些都是微凸起,所以它们不能支持很多的剪切应力。通过这些微凸起输入100瓦,但你不能把它们全部通过一个微凸起传输。你可能有一个100 x 100的区域,它们同时携带所有的能量。但如果有一些小问题,如凸隙或缩小的连接,一旦变热,焊料软化,没有足够的支持,整个芯片组装开始翘曲和转移从差分热膨胀。这是一个很大的问题。公司需要从机械性能上模拟这些三维组件在热应力和机械应力下的翘曲和弯曲,这直接影响了现场的可靠性和预期寿命。”

为了优化芯片封装性能,芯片设备制造商正专注于优化各种架构中的晶粒到晶粒或者晶粒到芯片封装连接,无论是垂直构建微凸起、混合粘接和桥接,还是水平构建扇形再分配层。决定如何以及在何处形成芯片互连将成为软件包集成的一个重要组成部分。

Imec3D芯片系统集成项目总监、高级研究员,研发副总裁Eric Beyne说:“在先进芯片封装中,我们需要一个非常高密度的芯片互连结构,从而把所有这些东西组成在一起,实际上是认为它仍然集成在一个芯片上,尽管有多个晶粒连接在一起.今天,人们花了很多努力来标准化芯片之间的通信,包括HBM、BoW(线束电线)或UCIe。这些标准需要提供关于如何在硅插入器、硅桥和高密度RDL之间结合的芯片设计技术指导方针,因为需要非常高密度的芯片互连来使它们在低功耗下工作。”

对于高性能芯片的应用,芯片之间的高带宽是必要的。Amkor技术公司负责芯片/FCBGA集成的副总裁Mike Kelly说:“如果你正在做一个更高带宽的两个芯片接口,它往往是一个宽的、低功耗的接口,需要相当高密度的介入器来实现这一点。这可能是芯片封装行业的关键区别。需要一个非常高密度的芯片集成方案,允许你连接晶粒,从而不会失去应有的性能。”

在今天的先进芯片封装中,热建模有助于找到潜在的故障点,但这并不是一个新问题。Ansys的Swinnen说:“如果你回到10000英尺的高度,看看电子系统,故障的两大原因是热和芯片互连故障。当然,它们都是相关的。热量常常导致互连故障。因此,芯片设计互连从一开始就是电子设计的一个弱点。”

其它的弱点也是最近才出现的。Ansys Sherlock的高级首席应用工程师Kelly Morgan说:“越来越多出现的故障机制是低k破解。在这种情况下,焊料在230摄氏度左右的温度下凝固,在芯片互连过程中低k电介质和焊料之间的CTE产生不匹配点,对超低k层施加拉应力,造成裂纹。”

化学和机械变化的模拟(见图1)在芯片设计过程的早期部分是有用的,可以防止此类问题。

图2:结构模拟确定了z高度的细微差异,这在多芯片集成中起着重要的作用。来源:Ansys

在最初的芯片设计阶段应考虑热和机械特征,最好地了解芯片封装系统的性能,特别是在温度、振动或恶劣环境条件下承受应力时。例如,即使两个晶粒并排放置可能会有不同的热运动,但它们之间的接近会导致它们的行为相似。

“当我们考虑芯片封装中的可靠性时,我们总是在考虑温度循环,”Amkor的 Kelly说。“你有CTE的差异,这就会在你冷却和加热时产生压力。通常情况下,晶粒会尽可能接近,芯片封装体积会导致成本增加。”

在半导体中,材料之间的相对CTE不匹配总是在不同的材料堆栈时造成头痛的问题。但是由于基板上的多芯片封装,特别是在非对称布局中,CTE不匹配会导致更严重的问题。

热膨胀系数是应力温度的反函数。最佳的CTE匹配是硅和硅(晶片的混合结合),或硅对硅插入器(SiO2/铜)之间。硅(2.5 ppm/K)和有机插入器(BT,CTE = 15-16 ppm/K)之间的CTE不匹配很大。

导电热界面材料(TIMs)通常夹在芯片封装和撒热器之间,为芯片系统中的传热提供良好的热路径。在装配加工和现场使用的温度变化过程中,晶粒、基板和集成散热器和散热器(盖)的cte不匹配,导电热界面材料可以散热并吸收一些应变。

对于TIMs有几种芯片设计材料解决方案,包括粘合剂、凝胶和润滑脂。大多数TIMs由聚合物基材组成,如环氧树脂或硅树脂,加上导电填料,如铝、氧化铝、氧化锌或银等。这些材料的优点是延申率高,加工性好。这些TIM材料的导热率被限制在10 W/m-K左右。工程师们正在评估更多的导电材料,如镓铟和镓铟锡合金,以及石墨烯,改进TIM技术。甚至金属 TIM也被广泛考虑,特别是对于高功率应用。

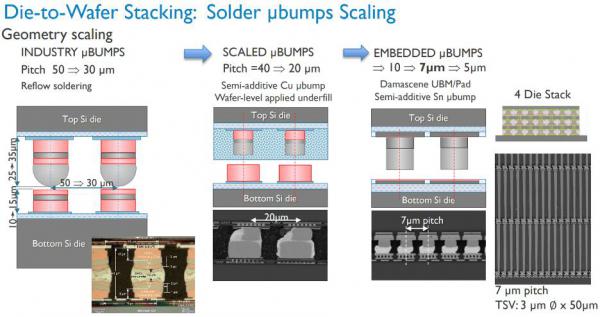

Solder为高级节点提供了挑战和解决方案。人们普遍认为,在10µm以下,芯片行业必须使用混合键来连接铜PAD位。

芯片行业展示了一种混合键合方法,如在10µm下的铜对铜直接键合。热压缩粘结(TCB)有助于实现高质量的焊缝结合,尽管压缩有助于克服内在的粘结。带有NCP/NCF(非导电膏体/薄膜)的TCB有助于解决大晶粒、小间距、/微管或预分配填充的挑战。

一个可能的缺点是,当间距变细时,迫使TCB中铜尖端和模具垫之间焊料突出,导致短路。

由于芯片设计互连方法的变化,就像混合连接的情况一样,在先进芯片封装推行的同时,公司正在联合起来解决制造问题。例如,UMC正在与Cadence、Winbond、Faraday和ASE合作,开发一个W2W(晶片到晶片)的3D-IC平台。通过结合供应商之间的芯片设计、制造、3D-IC、测试和芯片封装专业知识,该集团旨在增加3D挑战,包括垂直集成的芯片设计流程、晶圆对晶圆混合结合的对准,以及经过验证的3D堆叠测试和组装路径。该项目的目标是包括系统级验证在内的端到端解决方案。

扇出晶片级封装

与现有的倒装芯片封装方法相比,扇形芯片封装提供了优越的电气和热性能,路径略小和更薄。高密度扇形RDL有两种:芯片优先和芯片最后。这两者只是略有不同,但都有其优有弊。

在芯片中,首先将热释放载带应用到晶片上,然后选择已知的晶粒良品(KGD)放置在载体上。接下来,经过载体后成型,形成RDL,然后焊接完成。在RDL中,首先再次沉积释放层,然后是RDL。接下来是已知的良好模具定位,然后是过模过程、载体释放、焊球沉积和成型。

尽管从芯片产量的角度来看,芯片设计最后一种方法有显著的优势,但芯片优先是更成熟的方法。

那么,为什么OSAT会同时提供这两种流程呢?芯片设计优先的方法可以提供稍微更高的性能,因为芯片信号直接连接到RDL层。但芯片产量问题可以促使人们具体决定使用芯片-最后的FOWLP。目前,最小的微凸间距是55到40µm,35µm正在开发中。但首先使用芯片,你不需要微凸起,所以芯片设计间距可以降低到25µm。

与微凸块比例相关的芯片产量限制鼓励了直接连接铜PAD位的混合结合工艺的发展。但是混合动力结合的高成本和复杂性促使芯片设计研发工程师专注于制造较小的凸块。Imec预计,从今天的35µm左右到20µm水平,使用半添加剂的铜微碰撞方案。为了在10µm以下,使用锡凸块和Cu/Sn的PAD位连接。

Fig. 3: A path to smaller microbumps fabrication. Source: imec

图3:更小的微凸起制造的路径。来源:imec

Imec的Beyne说:“例如,我们可以发展20µm间距,而不是60µm。这立即将额外线路的长度和芯片上的面积减少了三倍。”

结论

对芯片集成的高密度芯片设计互连导致了更多可扩展的方法,包括微凸块尺寸和混合邦定。但是每个芯片封装都是定制的,这大大增加了芯片设计方面所需的工程工作量。随着芯片行业越来越熟悉硅和有机插入器、RDL扇形输出和嵌入式选项,可靠性特别是与热和机械分析相关成为优先事项。随着Cadence目前跨越设计、制造、测试和组装的芯片集成挑战,Cadence、UMC、Winbond和ASE之间的合作关系可能会变得更加普遍。即使是来自不同设备制造商的芯片,芯片行业将使封装中的芯片集成成为现实。

广告

广告

暂无评论